Zynq-7000 AP SoC by software reset

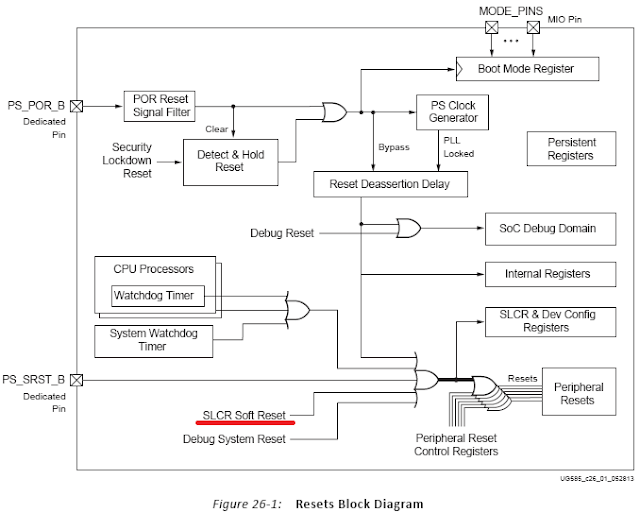

The reset system includes resets generated by hardware, watchdog timers, the JTAG controller, and software. Every module and system in Zynq-7000 AP SoC devices includes a reset that is driven by the reset system. Hardware resets are driven by the power-on reset signal (PS_POR_B) and the system reset signal (PS_SRST_B).

Just like the other system resets, all of the RAMs are cleared and the PL is reset as well.

Related register :

SLCR_LOCK

Relative Address : 0x00000004

Absolute Address : 0xF8000004

Width : 32 bits

Access Type : wo

Reset Value : 0x00000000

SLCR_UNLOCK

Relative Address : 0x00000008

Absolute Address : 0xF8000008

Width : 32 bits

Access Type : wo

Reset Value : 0x00000000

Description : SLCR Write Protection Unlock

SLCR_LOCKSTA

Relative Address : 0x0000000C

Absolute Address : 0xF800000C

Width : 32 bits

Access Type : ro

Reset Value : 0x00000001

Description : SLCR Write Protection Status

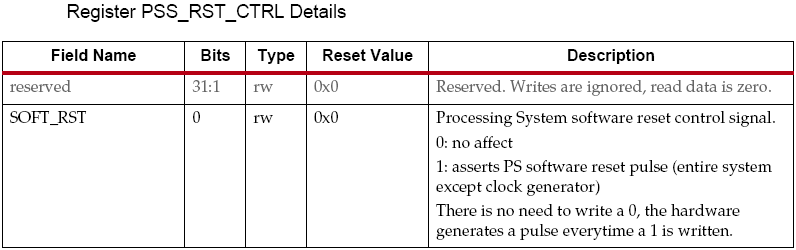

PSS_RST_CTRL

Relative Address : 0x00000200

Absolute Address : 0xF8000200

Width : 32 bits

Access Type : rw

Reset Value : 0x00000000

Description : PS Software Reset Control

reference file : ug585-Zynq-7000-TRM.pdf (chapter 26 : Reset System)

Relative Address : 0x00000008

Absolute Address : 0xF8000008

Width : 32 bits

Access Type : wo

Reset Value : 0x00000000

Description : SLCR Write Protection Unlock

SLCR_LOCKSTA

Relative Address : 0x0000000C

Absolute Address : 0xF800000C

Width : 32 bits

Access Type : ro

Reset Value : 0x00000001

Description : SLCR Write Protection Status

PSS_RST_CTRL

Relative Address : 0x00000200

Absolute Address : 0xF8000200

Width : 32 bits

Access Type : rw

Reset Value : 0x00000000

Description : PS Software Reset Control

reference file : ug585-Zynq-7000-TRM.pdf (chapter 26 : Reset System)

留言

張貼留言